What We Do

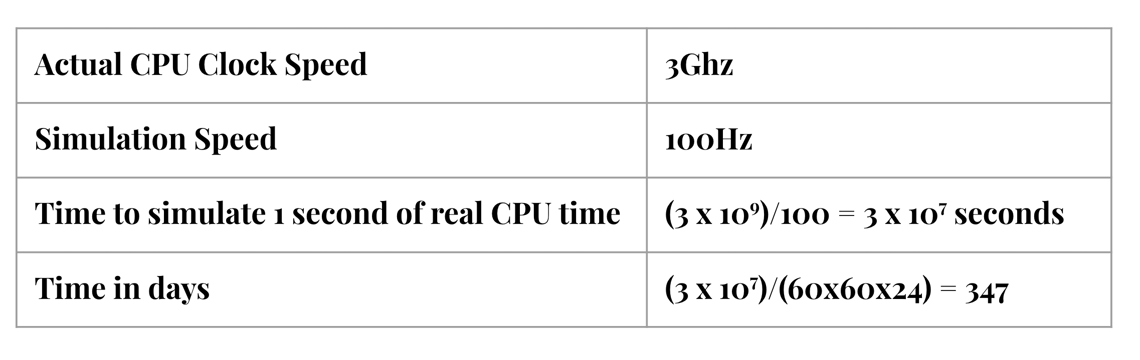

Modern computer processors can cost hundreds of millions of dollars and up to 4 years to design. A vast majority of the design cycle, 60 percent according to a credible industry survey*, is spent verifying the functionality of the processor. Another reason for the long design cycle is the slow speed of the Electronic Design Automation (EDA) tools deployed in the verification process. Simulation tools by EDA vendors simulate approximately 50-100 clock cycles of design time per second in the typical case. For a processor running at 3 gigahertz, it would take almost one year (see table below) to simulate what the processor can execute in 1 second.

We have built a solution that will dramatically reduce the duration of the design cycle and cost of computer processor design by attacking the two main time sinks of this cycle: Verification time and Simulation speed